iEW400 IP from Imagination Technologies lets you add the latest Wi-Fi connectivity to an FPGA, SoC, or ASIC, with focus on minimizing power consumption and increasing battery life.

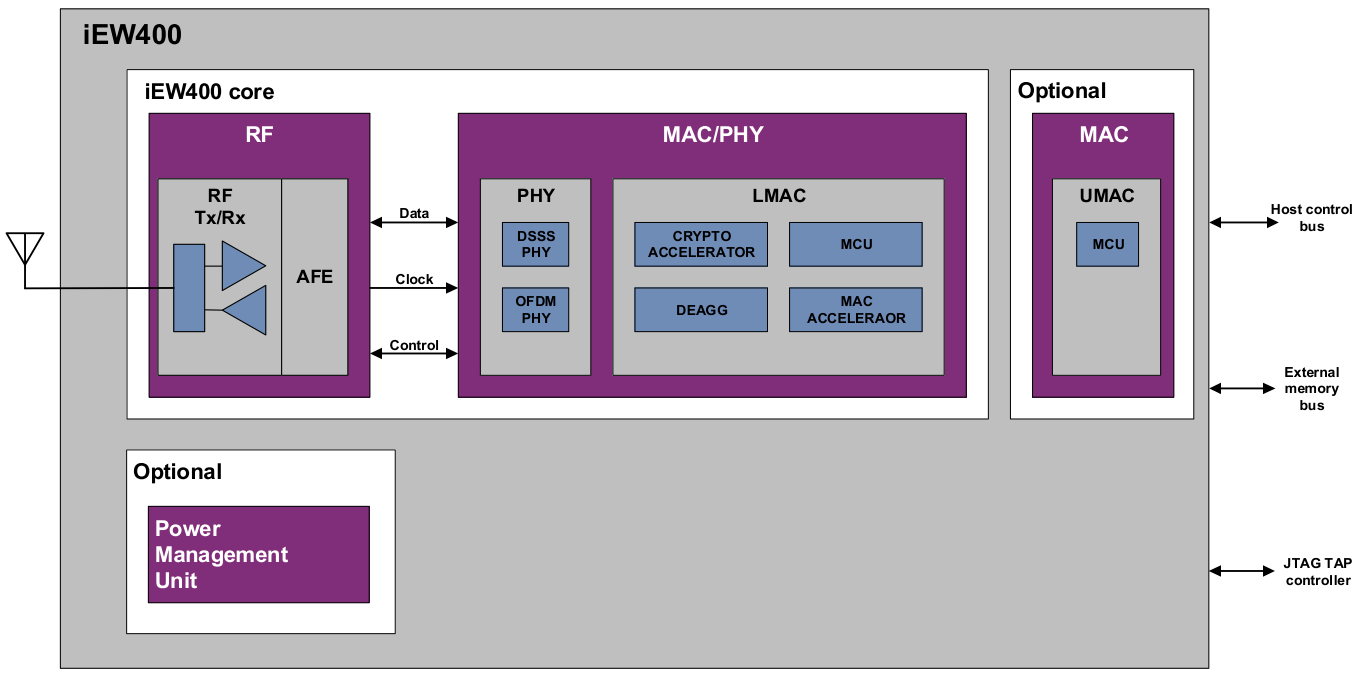

With of the high levels of integration needed in todays IoT devices and wearables, engineers need to embed connectivity into FPGAs, SoCs, and ASICs. Adding a separate chip to a board takes up too much space and consumes too much power. The iEW400 Wi-Fi 6 IP from Imagination Technologies adds the RF (2.4 GHz and 5 GHz), analog front end (AFE), baseband physical layer (PHY) and media access control (MAC) blocks to your design.

The iEW400 IP supports IEEE 802.11a/b/g/n/ac/ax single input/single output (SISO) with channel bandwidths of 20 GHz and 40 GHz. Because the iEW400 is designed for relatively low-speed IoT devices, the wider channel bandwidths supported by IEEE 802.11ac/ax are not needed.

The iEW400 IP supports IEEE 802.11a/b/g/n/ac/ax single input/single output (SISO) with channel bandwidths of 20 GHz and 40 GHz. Because the iEW400 is designed for relatively low-speed IoT devices, the wider channel bandwidths supported by IEEE 802.11ac/ax are not needed.

In terms of power consumption, the iEW400 IP uses optimized bit width, listen mode, ADC and DAC, automatic gain control (AGC), phase-locked loop (PLL), and power amplifier.

When used with Wi-Fi 6, the iEW400 IP takes advantage of Target Wake Time (TWT), a feature that negotiates when access points and devices awaken. Through pre-scheduling, a device won’t use excess energy while waiting to communicate with an access point, which can significantly increase battery life.

Related articles

Tell Us What You Think!