This week, at the 2023 International Solid-State Circuits Conference, imec presents a novel digitally calibrated charge-pump (CP) phase-locked loop (PLL) that can generate high-quality frequency-modulated continuous-wave (FMCW) signals for mmWave radars at low power consumption. The novel PLL is a critical building block for future short-range automotive (in-cabin and out-of-cabin) and industrial (e.g., on-cobot sensing) radar applications.

This week, at the 2023 International Solid-State Circuits Conference, imec presents a novel digitally calibrated charge-pump (CP) phase-locked loop (PLL) that can generate high-quality frequency-modulated continuous-wave (FMCW) signals for mmWave radars at low power consumption. The novel PLL is a critical building block for future short-range automotive (in-cabin and out-of-cabin) and industrial (e.g., on-cobot sensing) radar applications.

FMCW mmWave-based radar sensors are becoming increasingly popular for multiple automotive, healthcare, and industrial applications. FMCW radars transmit a sinusoidal wave whose frequency increases linearly in time, a sweep referred to as ‘chirp.’ After being reflected by the object, the signal is picked up by the receiver and mixed with the original chirp signal, after which the object’s distance and speed can be extracted. The quality of the radar signal depends largely on the performance of the PLL used to generate the chirp signal.

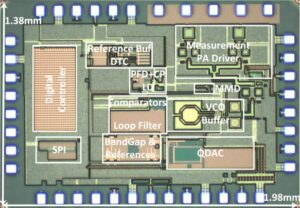

Imec’s novel PLL generates highly linear, high-quality chirp signals centered around 16GHz with a chirp bandwidth of 1.5GHz. A key achievement is reaching chirp speeds down to 12µs, with as low as 41kHzrms error in frequency modulation (rms-FM-error). The PLL enables extremely fast startup (below 1µs) and minimal reset time between chirps (1µs reset time). The chirp generator operates in duty-cycled mode – synthesizing N chirps in one burst before powering down – providing significant power savings. For example, the PLL consumes only 9.2mW and 1.48mW when operating in a 50 percent and one percent duty-cycled mode, respectively. Even after power-down mode, the rms-FM-error of the first chirp remains below 41kHz. The duty cycling performance was enabled by adopting a charge-pump (CP)-based PLL architecture, fabricated in 28nm CMOS technology and extended with a phase-offset compensation time-to-digital convertor (POC-DTC) to facilitate fast self-calibration.

Tell Us What You Think!