Gallium nitride (GaN) RF power amplifiers have improved efficiency and linearity in cellular base stations and military/aerospace systems. As these parts have matured and their reliability has improved, systems engineers are looking at GaN to offer advantages over traditional silicon-based implementations across a wide variety of new applications. Power conversion is a requirement common to almost every electronic system. Reducing losses in the power conversion process saves energy, lowers operating costs, lowers device temperatures and can improve system reliability. For example, removing the need for fans and reducing the size of heat sinks alone can justify the additional costs associated with incorporating GaN power devices. New classes of power GaN FETs up to 600V, and silicon carbide (SiC) FETs above 1200V, have been introduced into the marketplace. Higher switching frequency possibilities with GaN and SiC are driving the need for lower inductance packaging, higher frequency gate drivers, higher frequency controllers, and lower loss magnetics.

Nanosecond-switching capabilities, lower switching losses, and lower capacitances of power GaN and SiC devices, versus silicon, are enabling new power conversion approaches. One example is a GaN-based, single-stage buck conversion from 48V to 1.8V at 40 amps with efficiencies above 92 percent for server platforms. A higher voltage example is a single-stage, non-isolated (no transformer) buck DC/DC conversion from a 380V bus to 12V at 10 amps. For a 1 MHz converter to step down the voltage to this small of a VOUT/VIN ratio requires FET ON times of approximately 32 ns. This is not possible using 500V silicon power MOSFETs today without paying a very high penalty in switching losses. New architectures, such as bridgeless PFC’s are making use of the fact that GaN FETs have no intrinsic body diode and can be used to switch in bidirectional current-flow applications.

RF System Requirements

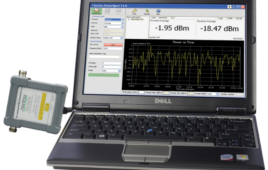

RF systems often have unique power requirements, such as a strong need for very quiet power rails or low-spurious output. Linear regulators provide the lowest noise approach, but the voltage drop across the device times the current through it must be dissipated as heat. Figure 1 shows a noise spectrum of a linear regulator used in many RF receiver designs. Integrating the voltage noise spectrum from 10 Hz to 100 kHz results in 4.17 uV rms or –94 dbm into 50 Ohms.

If higher currents or higher efficiencies are needed, hard-switching or resonant converters can be used to achieve efficiencies above 98 percent. However, converters often require extra filtering to remove switching noise and harmonics. GaN enables switching frequencies into the megahertz regime, pushing the switching noise out-of-band and can make filtering easier to implement. Increasing the switching frequency also allows wider band control loops to be used to regulate away input line or output load induced transients. It is interesting to look at GaN-based, high-frequency switching voltage conversion systems from a RF perspective to gain insight into improved performance options.

Phase Noise and Jitter

Phase noise is key parameter in RF oscillator designs and RF systems. In communication systems, phase noise, along with amplitude noise, determine signal-to-noise ratios (SNRs), symbol rates, and bit-error rates. In RF-sensing systems such as chirp frequency-modulated-continuous wave (FMCW) automotive radar, the phase noise of the oscillator determines how well close objects or tightly clustered objects (such as pedestrians) can be detected and tracked. More advanced synthetic aperture radar imaging and moving target indicator systems are also limited by the phase noise of their oscillators.

In digital systems, where timing is often a key parameter [1], the phase noise of the oscillator or clock is usually converted into a timing-centric term called jitter. It is important to remember that phase noise is a random process. Figure 2 shows the phase noise versus frequency spectrum from a very clean 10 MHz signal source. The analyzer integrates the phase noise from 100 Hz to 5 MHz and calculates a root-mean-square (rms) jitter value of 294 femtoseconds. The timing probability density function shown next to the screen shot is an example of what could be expected, if a large number of oscillator periods were sampled and compared to one another. A worst-case timing analysis using ±3 sigma of the time distribution (6 times the rms jitter) as a peak-to-peak jitter estimate is usually sufficient to determine bit error rates (BERs) or achieve timing closure in logic circuits. Many references show how an analog-to-digital (ADC) or digital-to-analog (DAC) converter’s noise performance is limited by the sampling clock jitter [2, 3].

RF Switching Power Supply Design

Switching power supply designs require a challenging combination of high-frequency analog, digital, magnetics, control theory, electromagnetic interference (EMI) and electromagnetic compatibility (EMC), and thermal engineering. With the advent of power GaN and nanosecond switching speeds, RF and microwave engineering is now needed to optimize next generation power conversion system performances. For example, an emerging standard called Alliance for Wireless Power (A4WP) is targeting >20W wireless (RF) power transfer at frequencies of 13.56 MHz (industrial, scientific, medical radio bands or ISM band).

GaN-based resonant designs with frequencies higher than 100 MHz are being researched for long-term evolution (LTE) envelope-tracking power as a way to improve linearity and efficiency. These and many other systems are demanding closer collaboration between RF engineers and traditional power supply design teams. RF layout techniques are already being used to reduce GaN power device packaging parasitics [4], and controlling parasitics is critical to achieve high-conversion efficiencies [5].

Figure 3 shows a simple buck regulator power stage. The term “buck” regulator comes from the fact that the inductor current is ramped up when Q1 is ON. Then when Q1 turns OFF, the current is pulled through D1 by the inductor until Q1 is again turned ON in the next cycle. For constant VIN, it is the duty cycle (D) equation that determines the output voltage. Time variations (jitter) in the duty cycle, TON or TP, will result in noise on the output voltage.

The spectrum of the output noise is a function of the lowpass L-Co filter that averages the switched square wave V waveform into a DC VOUT value. VOUT also has a non-random voltage ripple at the switching frequency, Fs (and odd harmonics), with a peak-to-peak amplitude that is a function of how much above Fs is from the filter cutoff.

Figure 4 shows a slightly more complicated switching power supply block diagram. The PWM controller processes the sensed output voltage and current and determines the PWM signal needed to regulate the power output (voltage or current).

Simple controllers typically have a relaxation (resistor) capacitor (RC) oscillator. This allows the designer an easy way to set the switching frequency and separate pins to determine dead times, current limits, and so on. RC oscillators, when compared to other oscillator designs, have the lowest Q. Therefore, these designs have the highest phase noise and the highest jitter. RC oscillators are limited in frequency range due to board parasitics and charge/discharge currents. Quartz crystal oscillators have very high Qs and the lowest phase noise. Ring oscillators, inductor-capacitor (LC) oscillators, microelectromechanical systems (MEMS) resonators, surface acoustic wave (SAW), and integrated bulk acoustic wave (BAW) resonators have been used to implement low-phase noise on chip circuits. Next generation controllers capable of running up to 20 MHz will need low phase noise oscillators to minimize the impact of jitter.

Wideband Control Loops

As GaN gains acceptance and higher frequency controllers and drivers become available, smaller L and C values can be used as output filters. Higher frequency lowpass filter cutoffs increase the frequency separation between where the control loop ends and the lowpass filter starts. Since noise power increases as a function of bandwidth, there is the potential for increased output noise in these higher frequency designs.

Control loop bandwidths in the MHz regime demand low propagation delays in the signal chain used to sense and process the output voltage and currents. Every 2.7 ns of propagation delay subtracts 10 degrees of phase shift at a switching frequency of 10 MHz. This also implies that every 2.7 ns of peak-to-peak jitter adds or subtracts 5 degrees of phase-shift from the control loop phase margin. Low propagation delays in the gate drivers and tight skew matching between dual-output drivers and tight dead time control will be required for next generation GaN based high frequency power converters.

Power GaN and SiC devices entering the marketplace are improving efficiencies, reducing the size of heat sinks, and allowing the removal of fans from some systems. The increased frequency possibilities are driving new requirements onto magnetics suppliers, controller and gate driver ICs. RF engineering talent and the lessons learned when designing RF and microwave systems is becoming the critical element to successful GaN-based power designs. Propagation delays, phase noise and jitter of existing power supplies must be improved to realize the potential for broad market GaN adoption. These are exciting times for power conversion design teams exploring GaN and SiC devices as ways to improve system performance.

References

- Clock and Timing Solutions, Texas Instruments, 3Q 2013

- Thomas Neu, Clock jitter analyzed in the time domain, Analog Applications Journal (SLYT379), Texas instruments, 3Q 2010

- Jitter and SNR Calculator for ADCs

- LMG5200 datasheet

- Layout considerations for LMG5200 GaN Power Stage, Application Report (SNVA729), Texas Instruments, March 2015