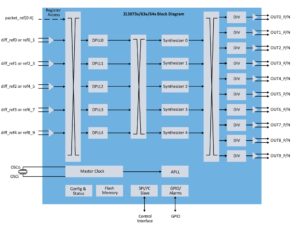

Microchip’s ZL30735 integrates eight DPLLs, five low-output jitter synthesizers, and an IEEE 1588-2008 protocol stack.

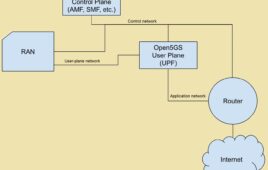

The splitting of radio access network functions creates an Open RAN that promises greater innovation and features in 5G networks. Splitting the traditional baseband unit into radio units (RU), distribution units (DU) and centralized units (CU) brings timing issues not present in an integrated RAN. Microship Technology addresses those issues with a series of timing ICs.

In Meet timing requirements in 5G networks Microchip’s Jim Olsen notes “the BBU is no longer a timing interface or demarcation point in 5G networks because it’s disaggregated into the Centralized Unit (CU) and Distributed Unit (DU) functional blocks in an Open RAN architecture.”

The latest addition to Microchip’s timing family, the ZL30735, combines eight independent DPLLs, five extremely low-output jitter synthesizers, and an IEEE 1588-2008 Precision Time Protocol Stack and Synchronization Algorithm software modules.

The latest addition to Microchip’s timing family, the ZL30735, combines eight independent DPLLs, five extremely low-output jitter synthesizers, and an IEEE 1588-2008 Precision Time Protocol Stack and Synchronization Algorithm software modules.

Microchip’s measure, calibrate and tune capabilities let 5G networks comply with International Telecommunication Union – Telecommunication (ITU-T) Standard G.8273.2 Class C (30 ns max|TE|) and the emerging Class D (5 ns max|TEL|) time error requirements. It also supports compliance for ITU-T G.8262, G.8262.1, G.813, G.812, Telcordia GR-1244, GR-253 and packet-timing compliance with ITU-T G.8261, G.8263, G.8273.2 (class A,B,C,D), G.8273.4.

The ZL30735 has five GPIO pins and an SPI or I2C processor Interface. It operates at VDD core voltages of 1.8 V and 3.3 V.

Tell Us What You Think!