Altera FPGAs enable designers of military communications systems to enhance security and speed packet inspection, among other applications. Altera will be in booth # 1007 at MILCOM 2015, being held in Tampa, Florida, from October 26 to 28. (PRNewsFoto/Altera Corporation)

Altera Corporation is demonstrating programmable logic-based security and system acceleration solutions for military grid communications, data centers, satellite communications and radar systems at MILCOM 2015 in Tampa, Florida, from October 26 to 28, 2015. Show attendees can see firsthand (Booth #1007) how Altera IP, FPGA, and SoC solutions enable product developers to address security and system acceleration requirements and control power consumption in a variety of military, aerospace and government communications systems.

Demonstrations from Altera and its ecosystem partners include the following technologies:

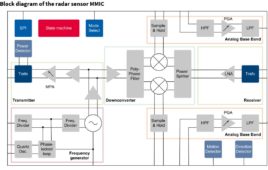

- A synthetic aperture radar (SAR) back-projection algorithm running on an Altera 20 nm Arria 10 FPGA, using the Altera OpenCL SDK flow and hardened IEEE 754-compliant DSP blocks for radar back-end processing

- Hardware and software security-hardened crypto accelerators

- A Snort neuromorphic processor demonstration running on Nallatech’s 385A Arria 10-based accelerator card for a 100-times performance gain in cyber security applications

- A software-defined radio (SDR) and SatCom development kit based on an Arria 10 SoC, Enpirion PowerSoCs, and Lime Microsystems’ field-programmable radio frequency MIMO transceiver, with real-time spectrum analyzer and 802.11 demonstrations

- A wideband SDR solution from 70MHz to 6GHz using an Altera Cyclone V SoC and Analog Devices’ AD9361 HSMC

- Several complete cognitive radio solution demonstrations from front-end tactical handhelds/portables to rack-mount systems, using the RedHawk SDR architecture and hardware acceleration with an OpenCL flow

- An ultra-wideband channelizer with JESD204B interface and signal generator feeding into a multi-GSPS (giga-samples per second) analog-to-digital converter (ADC)

- Multiple COTS subsystems and SOM modules from Altera ecosystem partners

Altera 20 nm FPGAs and SoCs Meet NSA IAD SIG Document Guidelines

Bolstering its support for military and government applications, Altera has completed the NSA’s Information Assurance Directorate (IAD) Secure Implementation Guidelines (SIG) process for 20 nm FPGAs and SoCs. This document provides unified government recommendations on the use of security settings in Altera FPGA and SoC products and how these products can be used most securely to mitigate security threats in system designs. The NSA IAD SIG describes design and data security features unique to Altera 20 nm FPGAs and SoCs and provides guidelines for security policies based on typical scenarios. NSA IAD SIG documents are now available from the NSA for Altera’s 28 nm and 20 nm FPGAs and SoCs. Altera is also working with the NSA IAD on SIG documents for 14 nm FPGAs and SoCs.