Designing 224 Gigabits per second four-level pulse amplitude modulation (224 Gbps-PAM4) interconnects is challenging. But it’s required to support the demands of generative artificial intelligence (AI), machine learning (ML), 1.6 Terabits per second (Tbps) networking, and other high-speed applications in advanced data centers, as well as 5G and 6G communications infrastructure.

At these elevated data rates, printed circuit board (PCB) traces, even using expensive high-performance laminates, are severely challenged to deliver the needed performance.

Instead, various wired and optical connector options are being developed and deployed. This FAQ reviews some of the 224 Gbps-PAM4 interconnect approaches being put forward and, along the way, looks at the convergence of high-speed cables and integrated circuit packages that may provide more options for 224 Gbps-PAM-4 interconnects.

For 224 Gbps applications, the performance of copper interconnects is being improved. Passive copper direct attach cables (DACs) are increasingly being replaced with active copper cables (ACCs) that include re-drivers and active electrical cables (AECs) that include re-timers and with new cable/connector geometries that reduce losses in the signal channel. These copper-based solutions are also challenging optical interconnects in several areas since they help reduce or more evenly distribute thermal dissipation through the system.

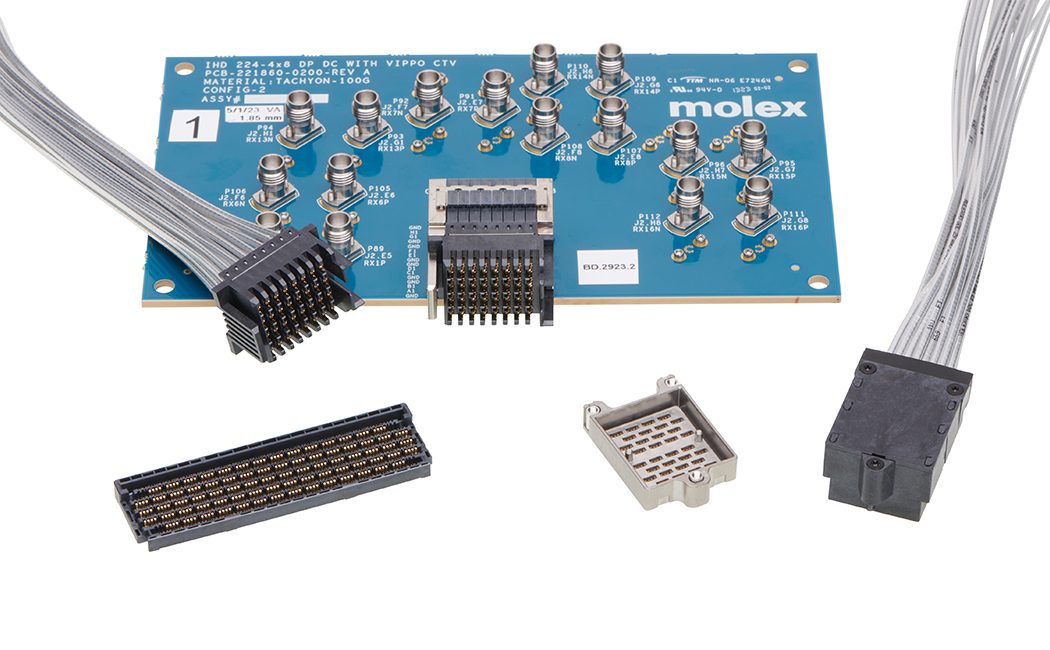

Convergence between mezzanine and backplane designs can support new architectures. Direct chip-to-chip solutions, near-ASIC connector-to-cable solutions, and new approaches for board-to-board connectivity are being developed. Some examples include (Figure 1):

- Genderless mezzanine board-to-board connectors that support 224 Gbps-PAM4 signaling and are available in several heights to support a range of PCB spacing requirements

- Connectors that meet the Open Accelerator Module (OAM) standard from the Open Accelerator Infrastructure Group, a subgroup of the Open Compute Project (OCP)

- Genderless backplane system that provides improved application flexibility while supporting 224 Gbps-PAM4 performance. It’s based on a surface-mount launch that simplifies integration and can accommodate a range of wire gauges for internal and external uses for optimal signal channel performance

- Near-ASIC connector-to-cable systems using high-performance shielded twinax for a high level of Tx/Rx isolation and with a fully protected mating interface and integrated strain relief to ensure reliable 224 Gbps-PAM4 connections

Figure 1. Examples of the numerous solutions being developed for 224 Gbps-PAM4 interconnects (Image: Molex).

Convergence and micro twinax

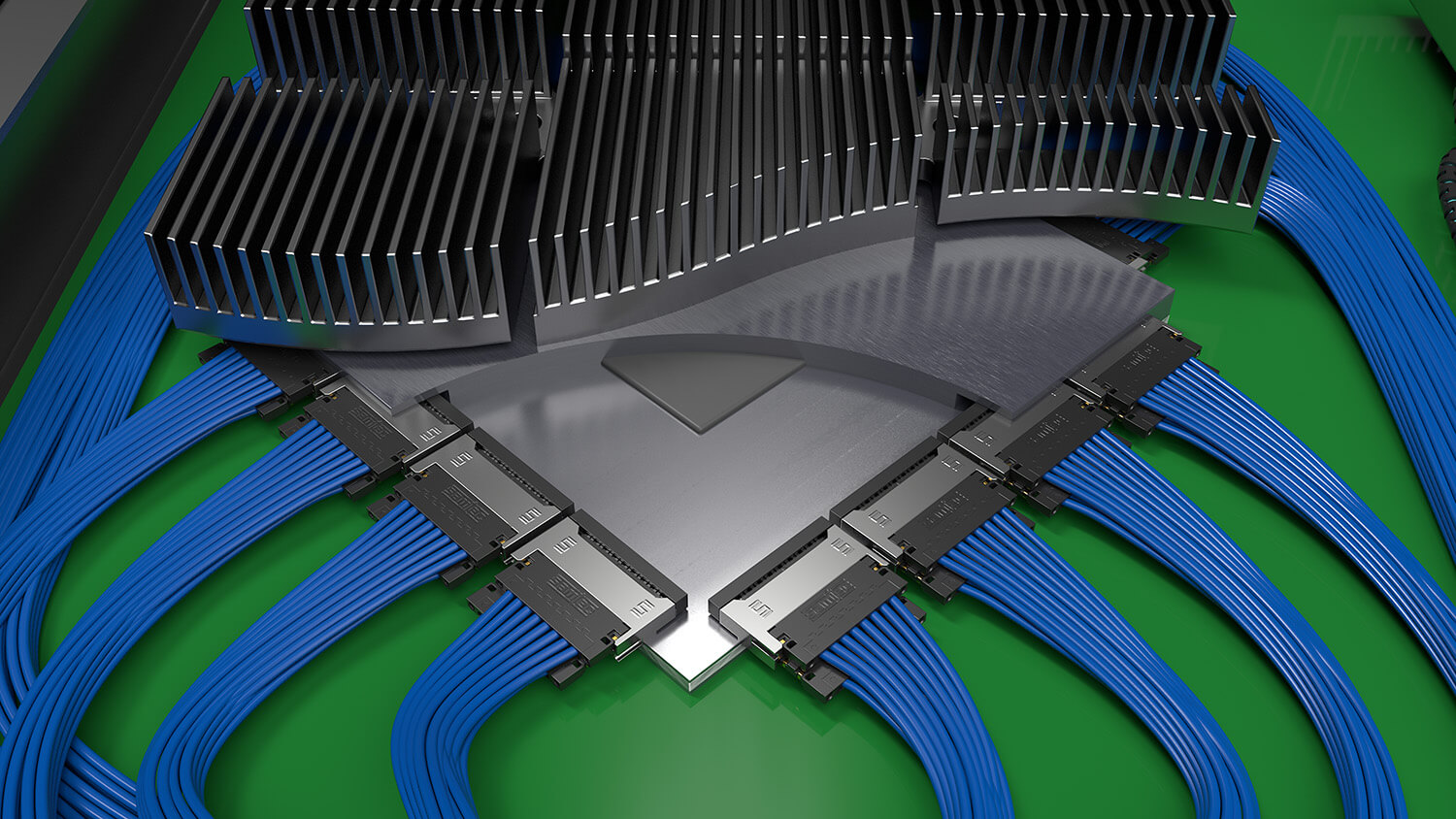

Current micro-twinax solutions support 112 Gbps PAM4 data rates. Increasing that to 224 Gbps will require a new approach that removes much of the loss from the signal channel. Even if not mandatory for 256 Gbps solutions, directly attaching the micro twinax cable to the ASIC substrate may prepare the way forward for faster signaling beyond 256 Gbps (Figure 2).

Current ASICs can support up to 256 lanes/512 dynamic paths (DP) of 112 Gbps, totaling 25.6 TB of throughput. Next-generation ASICs will double the data rate to 224 Gbps. Attaching the micro-twinax cable directly to the ASIC substrate is expected to reduce package and break-out-related losses. Reaching that goal will require converging micro-twinax cable technology with advanced IC packaging and on-package interconnects and new approaches to ASIC I/O design.

Figure 2. Convergence of multiple technologies is expected to enable directly attaching micro twinax cables to ASIC packages for ultra-high-speed connectivity (Image: Samtec).

Existing 112 Gbps-PAM4 direct ASIC attached cable systems can support 25.6 TB aggregate data rates and are expected to provide a path for the development of 256 Gbps solutions. The existing solutions support a 22-inch reach using the IEEE 802.3ck allowable loss limits. That compares with a 4.5-inch reach using traces on a Megtron7 PCB. The system is being refined to support 256 Gbps-PAM4 copper interconnects and is being designed to support future requirements for optical connectivity.

Summary

224 Gbps-PAM4 signaling is the next step in the development of ever-faster connectivity for advanced data center applications and 5G and 6G communications. Several options have already emerged, and more are expected. A key in many cases is the convergence of multiple technologies like advanced IC packaging, on-package interconnects, and new approaches to ASIC I/O designs.

References

Tell Us What You Think!